KiviHash-SHA3 Overview

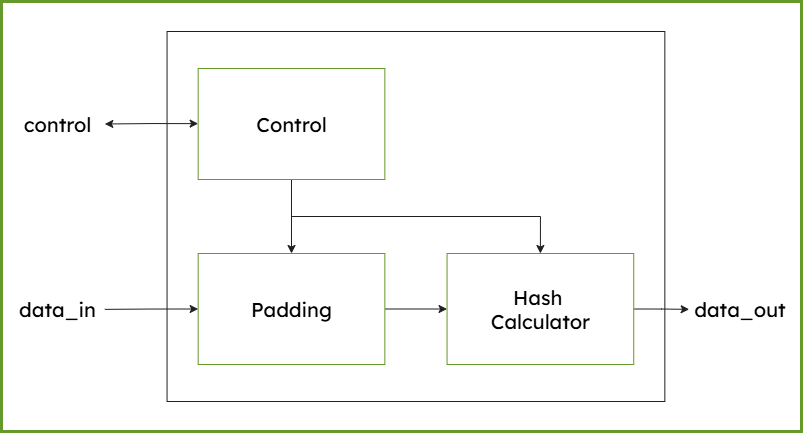

The KiviHash-SHA-3 (secure hash algorithms) is a hardware accelerator for cryptographic hashing functions. It is an area efficient and high throughput design and compliant to NIST’s FIPS 202 standard. It supports all SHA-3 hash functions (SHA-3-224, SHA-3-256, SHA-3-384 and SHA-3-512) as well as extendable output functions (XOF), SHAKE-128 and SHAKE-256. It provides full protection against time-based side channel attacks (SCA). Automatic byte padding is included. It operates in a single clock domain and has been extensively verified.

Key Features

- NIST FIPS 202 compliant

- Supports cryptographic hashing for SHA-3 in 224/256/384/512 mode

- Supports cryptographic hashing for Keccak in 224/256/384/512 mode

- Extendable-Output Functions for SHAKE 128/256

- AMBA® AXI4-Lite Interface

- Fully synchronous design

- HAL and software driver (C-code, platform independent)

- Platform agnostic design for any FPGA

Easy integration

- AMBA® AXI4 lite Interface

- Platform agnostic C source code HAL, API and software driver

- Software examples included

- Software user guide

- Integration examples

- Comprehensive documentation

Applications & Use Cases

- Firmware Updates: Detecting tampered or corrupted update packages

- FPGA bitstreams: Ensuring only trusted configurations are loaded

- External memory integrity: Protecting stored data in flash or external RAM

Test and Verification

- NIST CAVS test vectors for SHA3 hash functions

- NIST CAVS test vectors for SHA3 XOF functions

- Extended verification through simulation

- FPGA integration and implementation tests

- Unity tests for driver and whole IP Core

Next steps

Download the product brief, request documentation, or schedule a technical discussion to review your architecture.

Licensing & Deliverables

| License type | Purpose | Scope | Fee | Deliverables |

| Product License | Manufacture of products intended for commercial distribution. | Valid for single-instance implementation/synthesis into one device (e.g., one type of SoC, or FPGA) for a specific project or product definition. Multiple instantiations refer to the physical realization of one IP core multiple times in one device. Product licenses for IP Cores include volume caps of 10,000 units for FPGAs. | One-time fee |

|

| Evaluation License | Usability and evaluation for upcoming design | Valid for single-instance implementation/synthesis into one device (SoC, or FPGA) for a specific upcoming design project. | Free, no license fee |

|

Support and Maintenance

- Maintenance & updates of IP cores included

- Rapid update/bug fix cycles

- Integration support: Comprehensive documentation and integration examples

- Web-based support with response times within 8 hours (Mo-Fri)

AMD (Xilinx) Implementation Results

|

Device

|

LUTs |

max. Frequency (MHz) |

max. Throughput (Gbps) |

|

Spartan 7 |

7687 | 171.5 | 8.4 |

|

Kintex 7 |

7722 | 258.5 | 12.4 |

|

Zynq US+ MPSoC |

7730 | 340.5 | 16.3 |

|

Versal AI Cores Series |

7572 | 427.4 | 20.5 |

Efinix Implementation Results

|

Device

|

XLR |

max. Frequency (MHz) |

max. Throughput (Gbps) |

|

Titanium |

9246 | 375.7 | 18.0 |

|

Topaz |

9246 | 234.6 | 11.3 |

|

Trion |

9246 | 102.9 | 4.9 |